# COMPILER CRYPTOSYSTEM CO-DESIGN

by

# Raghav Malik

# A Dissertation

Submitted to the Faculty of Purdue University

In Partial Fulfillment of the Requirements for the degree of

# **Doctor of Philosophy**

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

Dr. Milind Kulkarni, Chair

School of Electrical and Computer Engineering

Dr. Benjamin Delaware

School of Computer Science

Dr. Tiark Rompf

School of Computer Science

Dr. Xiaokang Qiu

School of Electrical and Computer Engineering

Approved by:

Dr. Milind Kulkarni

Cancel me not - for what then shall remain?

Abscissas some mantissas, modules, modes,

A root or two, a torus and a node:

The inverse of my verse, a null domain.

Ellipse of bliss, converge, O lips divine!

The product of our scalars is defined!

Cyberiad draws nigh, and the skew mind

Cuts capers like a happy haversine.

I see the eigenvalue in thine eye, I hear the tender tensor in thy sigh. Bernoulli would have been content to die, Had he but known such  $a^2 \cos 2\varphi$

From "Love and Tensor Algebra," Stanislaw Lem

# ACKNOWLEDGMENTS

It is, I think, traditional to start the acknowledgments of a dissertation with some pithy phrases that point out how difficult a PhD is to complete alone, how vital it is to have a good support system, and so on. While I'm certain I knew all these facts academically before starting my degree, its only now, as I look back over the past six years, that I realize how much this was truly a group effort—I don't think I could have been even a tenth as successful if I hadn't been lucky enough to be surrounded by a loving and supportive family, a wonderful group of friends and colleagues, and an incredible advisor. The degree may have my name on it, but it is as much their accomplishment as mine.

The actual list of people I'd like to thank here is far longer than what the space allows; what follows is my best approximation thereof. First and foremost, I'd like to thank my family, who have been immensely supportive throughout this endeavor. From my parents, who have been there at every turn to celebrate my successes and soften the blow of my many failures, to my little brother, who insists on accepting credit for reading the many drafts I've sent his way, to my grandparents, who I am certain are even more excited than I am at my finally graduating, I truly could not have done this without them.

I'd like to thank my D&D groups over the years for injecting some much-needed whimsy into my life: Morana, Guthard, Trym, Margaret, Ciru, Wern, Claire, Aster, Willow, Lark, Hickory, Fig, Rosalia, and many others; I won't soon forget the stories we made.

I'd like to thank Amy, Adam, and all my orchestra stand partners and chamber group-mates, including, Riley, Ben, Janhavi, Andrew, Kevin, Sreesha, Elle, Maggie, and Allison, for allowing me to continue enriching my life with music and for providing welcome distractions and outlets when research became too stressful.

I'd like to thank my labmates, Vani, Durga, Pratyush, Aditha, Krish, Charitha, Dulani, Vickrant, Artem, Vidush, Fouad, and Vedant, for helping create a welcoming and exciting work environment. I will miss the hours spent in front of whiteboards, the group dinners and discussions, and the countless post-deadline nights at Knickerbocker and the Spot.

I'd like to thank Anja, David, Tiana, Pranesh, Ilan, Abhi, and Jenna, for helping me discover a love of teaching, and for listening to my innumerable rants about C++.

I'd like to thank Omar, Kurt, Sonya, Camille, Sunidhi, Jenna, Sara, Anja, Pratyush, Patrick, Dharun, Aditi, Alex, Juli, Nicole, and Jacob, for being amazing friends, for putting up with me for so long and for allowing me to have some semblance of a social life.

I'd like to thank Donnie for reminding me about Stirling's Approximation at every opportunity.

I'd particularly like to thank Sofia, Manuel, Francille, Ben, and Qianchuan, for engaging with and encouraging my slow descent into category-theoretic madness, despite many others' best efforts to the contrary.

I'd like to thank the members of my committee, Ben, Tiark, and Xiaokang, for their feedback and advice over the years; this document would be far less polished without it.

Finally, I'd like to thank Milind. I am convinced that one's PhD advisor contributes much more to one's experience than the topic of one's dissertation, and I don't think I could have asked for a better advisor than Milind. When I started my degree I had no idea I wanted to do PL, or even what PL really entailed; I just knew the project he had in mind sounded interesting, and I wanted to work with the professor who taught me C all those years ago. Over the years, he has infected me with his enthusiasm for the subject and for academia, helped me develop my own research ideas and writing style, roasted me (probably less than I deserve) for constantly bringing up category theory, and molded me into the researcher I am today. I am grateful for the chance to have been one of his students.

This work was supported by the National Science Foundation grants CCF-2216987, CCF-1919197, CCF-1908504, CCF-1725672, the Office of the Director of National Intelligence, Intelligence Advanced Research Projects Activity, contract #2019-19020700004, and Cisco.

# TABLE OF CONTENTS

| LIST OF TA  | BLES                       |

|-------------|----------------------------|

| LIST OF FIG | GURES                      |

| ABBREVIAT   | TIONS                      |

| GLOSSARY .  |                            |

| ABSTRACT    |                            |

| 1 INTRODU   | JCTION                     |

| 1.1 Lang    | guages & Compilers for MPC |

|             | ributions                  |

| 2 BACKGR    | OUND                       |

| 2.1 Vecto   | orization                  |

|             | sion Forests               |

|             | Homomorphic Encryption     |

| 2.3.1       |                            |

| 2.3.2       |                            |

| 2.3.3       |                            |

| 2.4 MLII    | R/HEIR                     |

|             | uits & Multiplexers        |

| 3 COYOTE    | 32                         |

|             | ote Overview               |

| -           | Compilation                |

| 3.1.2       | 1                          |

| 3.1.3       |                            |

| 3.2 Vecto   | orization Procedure        |

| 3.2.1       |                            |

| 3.2.2       |                            |

| 3.2.3       |                            |

| 3.2.4       |                            |

| 3.2.5       |                            |

|   | 3.3 | An eD   | SL and Compiler for FHE Programs        | 47 |

|---|-----|---------|-----------------------------------------|----|

|   |     | 3.3.1   | Code Generation                         | 48 |

|   | 3.4 | Evalua  | ting Coyote                             | 49 |

|   |     | 3.4.1   | Computational Kernels                   | 50 |

|   |     | 3.4.2   | Costs and Effects of Vector Compilation | 51 |

|   |     | 3.4.3   | Speedups                                | 53 |

|   |     | 3.4.4   | Scalability                             | 54 |

|   |     | 3.4.5   | Randomly Generated Irregular Kernels    | 55 |

|   |     | 3.4.6   | Comparison to Hand-Optimized Schedules  | 57 |

|   |     | 3.4.7   | Effects of Data Layout                  | 58 |

|   |     | 3.4.8   | Effects of Search and Co-Optimization   | 58 |

|   |     | 3.4.9   | Optimality Tradeoffs from Timeouts      | 61 |

|   | 3.5 | Other   | SLP Vectorizers                         | 61 |

|   |     |         |                                         |    |

| 4 | COF |         |                                         | 63 |

|   | 4.1 | COPSI   | E Overview                              | 65 |

|   |     | 4.1.1   | The Players                             | 65 |

|   |     | 4.1.2   | The Workflow                            | 66 |

|   |     | 4.1.3   | The Evaluation Algorithm                | 66 |

|   | 4.2 | Definit | ions & Preliminaries                    | 70 |

|   |     | 4.2.1   | Properties of Decision Trees            | 70 |

|   |     | 4.2.2   | Data Representation and Key Kernels     | 72 |

|   | 4.3 | The Co  | OPSE Algorithm                          | 73 |

|   |     | 4.3.1   | Algorithmic Primitives                  | 73 |

|   |     | 4.3.2   | Algorithm                               | 75 |

|   | 4.4 | Compi   | ler & Runtime                           | 76 |

|   | 4.5 | Comple  | exity Analysis                          | 78 |

|   | 4.6 | Securit | y Properties                            | 80 |

|   |     | 4.6.1   | Information Leakage                     | 80 |

|   |     | 4.6.2   | Security Implications of COPSE design   | 82 |

|   | 4.7 | Evalua  | ting COPSE                              | 84 |

|   |     | 4.7.1   | Benchmarks, Configurations, and Systems | 84 |

|   |     | 4.7.2   | COPSE Performance                       | 85 |

|   |     | 4.7.3   | Different Party Setups                  | 87 |

|   |     | 4.7.4   | Evaluation on Microbenchmarks           | 88 |

|   |     |         |                                         |    |

| 5 | COI  | L      | 92                                               |

|---|------|--------|--------------------------------------------------|

|   | 5.1  | COIL   | Overview                                         |

|   |      | 5.1.1  | Building a Path Forest                           |

|   |      | 5.1.2  | COIL Program = Computation + Decision Tree       |

|   |      | 5.1.3  | COIL Discovers Good Implementations              |

|   | 5.2  | Langu  | age Syntax & Semantics                           |

|   |      | 5.2.1  | Language Design                                  |

|   |      | 5.2.2  | Compilation                                      |

|   |      | 5.2.3  | Optimizations on Path Forests                    |

|   |      | 5.2.4  | Recursive Functions                              |

|   |      | 5.2.5  | Re-Folding                                       |

|   |      | 5.2.6  | Generating Code                                  |

|   | 5.3  | Imple  | menting COIL                                     |

|   |      | 5.3.1  | Efficient Decision Tree Evaluation via COPSE     |

|   |      | 5.3.2  | Choice of FHE Scheme                             |

|   | 5.4  | Evalua | ating COIL                                       |

|   |      | 5.4.1  | How efficient are the programs COIL generates?   |

|   |      | 5.4.2  | How does COIL compare to known custom protocols? |

|   |      | 5.4.3  | Where do COIL's speedups come from?              |

|   |      | 5.4.4  | The advantage of decision tree conversion        |

|   | 5.5  | Scalin | g & Other Concerns                               |

|   |      | 5.5.1  | Path Explosion                                   |

|   |      | 5.5.2  | Blocking                                         |

|   |      | 5.5.3  | Other Path-Sensitive Analyses                    |

|   | 5.6  | Other  | Ways of Dealing With Control Flow                |

|   |      |        | Compiling Oblivious Control Flow                 |

|   |      | 5.6.2  | Reducing Control Flow                            |

| c | 00.4 | V CDT  | 100                                              |

| 6 | COA  |        |                                                  |

|   | 6.1  |        | iew                                              |

|   |      | 6.1.1  | Some Intuition for Arithmetic LUTs               |

|   |      | 6.1.2  | Compiling Boolean FHE Programs                   |

|   | _    | 6.1.3  | Doing Better with COATL                          |

|   | 6.2  |        | ng Circuits with Arithmetic LUTs 128             |

|   |      | 6.2.1  | Arithmetic LUT Formalism                         |

|   |      | 6.2.2  | Building Lookup Tables                           |

|    |      | 6.2.3  | Finding Gates to Merge        |

|----|------|--------|-------------------------------|

|    |      | 6.2.4  | A Small Example               |

|    | 6.3  | Implen | nentation Details             |

|    |      | 6.3.1  | Unrolling Secret Loops        |

|    |      | 6.3.2  | OpenFHE Code Generation       |

|    | 6.4  | On Sca | alability                     |

|    |      | 6.4.1  | Algorithmic Complexity        |

|    |      | 6.4.2  | Applying COATL to Subcircuits |

|    | 6.5  | Evalua | ting COATL                    |

|    |      | 6.5.1  | Efficiency of Generated Code  |

|    |      | 6.5.2  | Impact on Compilation Time    |

|    |      | 6.5.3  | Scaling to Larger Inputs      |

|    |      | 6.5.4  | Kernelization                 |

|    |      | 6.5.5  | Impact of Solver Timeout      |

| 7  | FUT  | URE W  | VORK                          |

|    | 7.1  | Compi  | ler Cryptosystem Choreography |

|    | 7.2  | Bootst | rapping-Aware Compilation     |

| RI | EFER | ENCES  | \$                            |

# LIST OF TABLES

| J.1 | code, and the ideal speedup (work/span)                                                                                                                                                               | 52  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Coyote vectorization vs. expert-written code                                                                                                                                                          | 57  |

| 3.3 | Comparison of compilation time (seconds) and vectorization speedup with vs. without synthesis timeouts.                                                                                               | 60  |

| 4.1 | Operation counts and multiplicative depth for COPSE                                                                                                                                                   | 79  |

| 4.2 | Total Evaluation Complexity                                                                                                                                                                           | 80  |

| 4.3 | Data revealed to each notional party in two-party configurations                                                                                                                                      | 80  |

| 4.4 | Data revealed to each party in three-party configurations                                                                                                                                             | 80  |

| 4.5 | Optimal encryption parameter values                                                                                                                                                                   | 85  |

| 4.6 | Microbenchmark specifications                                                                                                                                                                         | 88  |

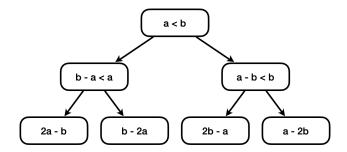

| 5.1 | Speedups of COIL over naive and expert implementations. Note that some numbers are missing: the naive merge times out, and we do not have an expert implementation available for second-price auction | 114 |

| 5.2 | COIL compile times broken down by stage                                                                                                                                                               | 114 |

| 5.3 | Breakdown of time spent evaluating decision tree branches vs. labels in the generated code                                                                                                            | 119 |

| 6.1 | Optimized and unoptimized benchmark run time, in milliseconds                                                                                                                                         | 144 |

| 6.2 | Optimized and unoptimized benchmark gate counts                                                                                                                                                       | 146 |

| 6.3 | Compile time statistics (in seconds) of unoptimized vs optimized benchmarks. Note that the reported COATL time includes the base HEIR compilation as well as the solver time                          | 147 |

| 6.4 | Kernel and Total gate counts of two different kernelizations of $4 \times 4$ matrix multiply                                                                                                          | 148 |

| 6.5 | Compilation and running times of kernelized $4 \times 4$ matrix multiply                                                                                                                              | 148 |

# LIST OF FIGURES

| 1.1 | Compiler Cryptosystem Co-Design can bridge the gap between sophisticated but crypto-agnostic compiler analyses, and modern cryptosystems with rich capabilities.                                                                                                                           | 18 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Example decision tree                                                                                                                                                                                                                                                                      | 26 |

| 3.1 | An example of an arithmetic circuit                                                                                                                                                                                                                                                        | 32 |

| 3.2 | Possible schedules for Figure 3.1                                                                                                                                                                                                                                                          | 33 |

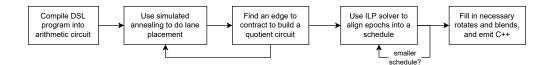

| 3.3 | High-level compilation steps                                                                                                                                                                                                                                                               | 36 |

| 3.4 | A running example of how Coyote vectorizes arbitrary arithmetic circuits                                                                                                                                                                                                                   | 36 |

| 3.5 | Coyote program for multiplying a vector by a matrix                                                                                                                                                                                                                                        | 38 |

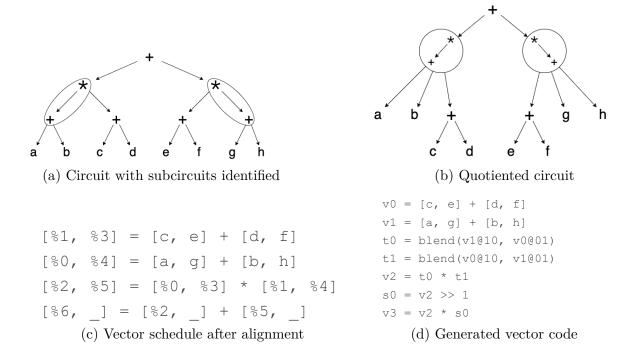

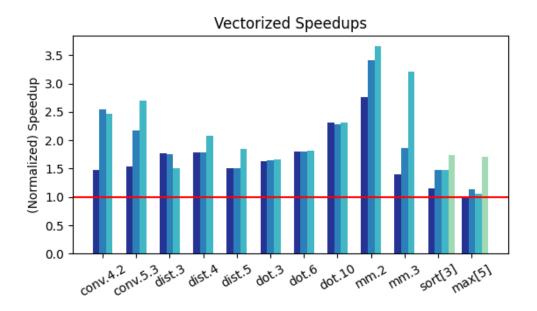

| 3.6 | Speedup of vectorized code over scalar (higher is better). Left-to-right, the first three bars for each benchmark represent unreplicated, partially replicated, and fully replicated inputs, respectively. The fourth bar for the sort[3] and max[5] benchmarks represent ungrouped inputs | 54 |

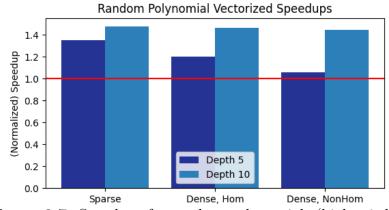

| 3.7 | Speedups for random polynomials (higher is better).                                                                                                                                                                                                                                        | 55 |

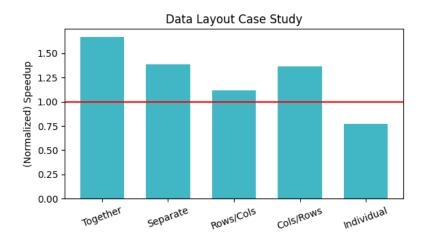

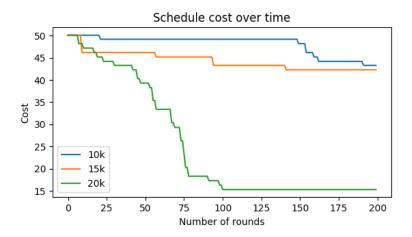

| 3.8 | Speedups for the five data layout case studies (higher is better). Note that the second bar ("Separate") corresponds to the leftmost bar of $mm.3$ in Figure 3.6                                                                                                                           | 59 |

| 3.9 | Schedule cost over time (lower is better) for different numbers of simulated annealing iterations for data layout per step of scheduling                                                                                                                                                   | 59 |

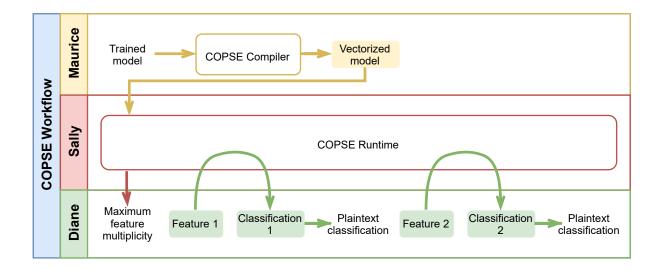

| 4.1 | High-level COPSE system workflow. Yellow components and data are Maurice's responsibility. Red components are Sally's. Green components are Diane's. Shaded boxes represent encrypted data                                                                                                 | 66 |

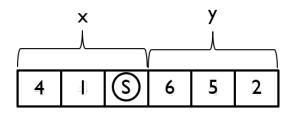

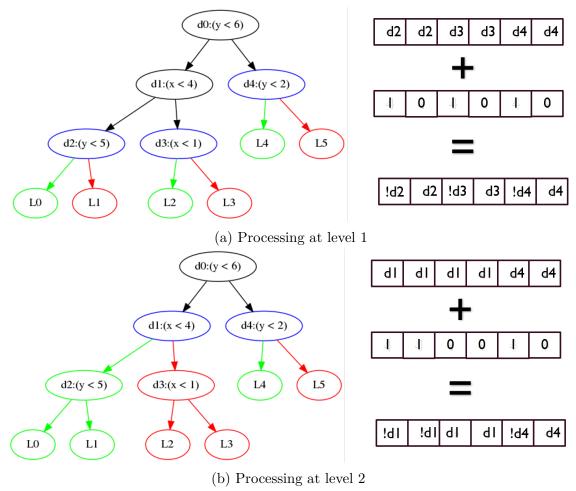

| 4.2 | Illustration of vectorized comparison step                                                                                                                                                                                                                                                 | 68 |

| 4.3 | Each level is processed individually                                                                                                                                                                                                                                                       | 69 |

| 4.4 | Level vectors are multiplied to yield the final result                                                                                                                                                                                                                                     | 70 |

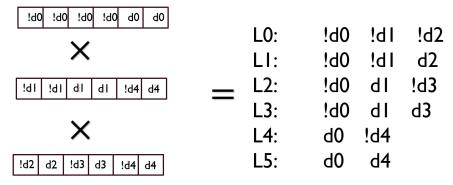

| 4.5 | Run time of microbenchmarks                                                                                                                                                                                                                                                                | 86 |

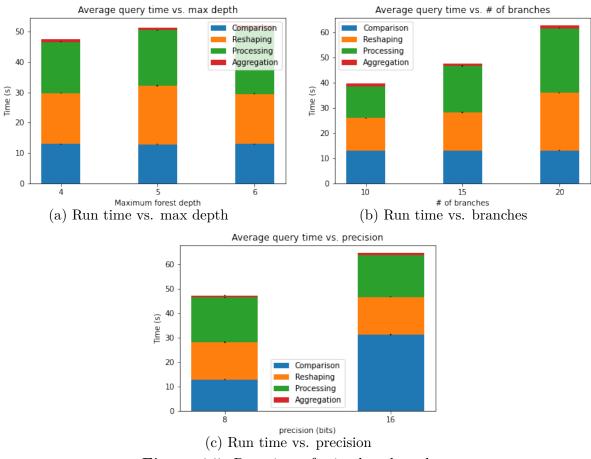

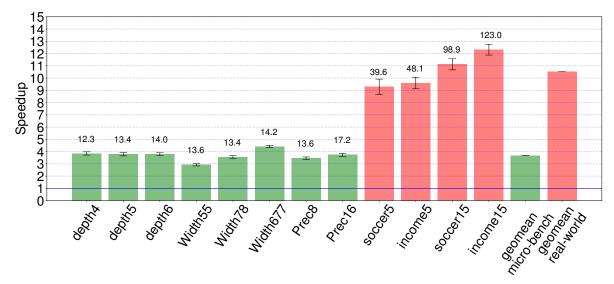

| 4.6 | Speedup of COPSE-compiled models over our implementation of Aloufi, et. al [42] when both are single-threaded. The number on top of each bar is the median running time (in milliseconds) for that model using COPSE                                                                       | 88 |

| 4.7 | Speedup that COPSE-compiled models experience when multithreaded instead of single-threaded. The number on top of each bar is the median run-time (in milliseconds) for multithreaded inference                                                                                            | 89 |

| 4.8 | Speedup of COPSE-compiled models over our implementation of Aloufi, et. al [42]. when both are multithreaded. The number on top of each bar is the median runtime (in milliseconds) for multithreaded COPSE.                                                                               | 90 |

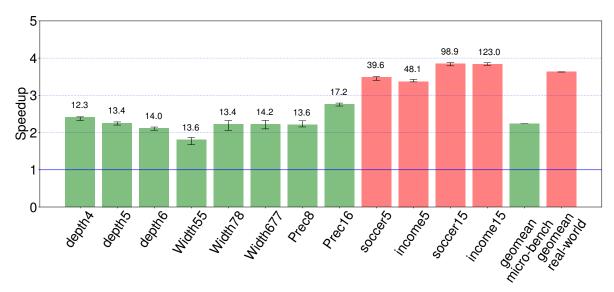

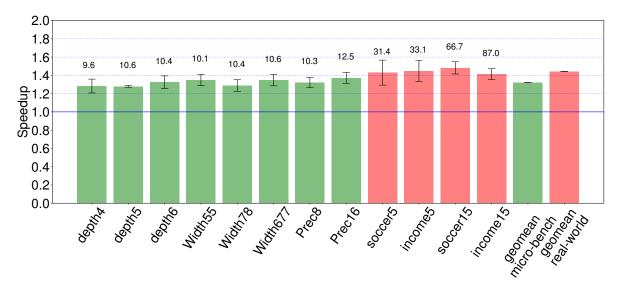

| 4.9  | Speedup of inference queries executed on plaintext models (when Maurice = Sally) compared to encrypted models (when Diane = Maurice). The number on top of each bar show the median inference run-time (in milliseconds) on the plaintext models                                                                                                                                                                                                 | 90   |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

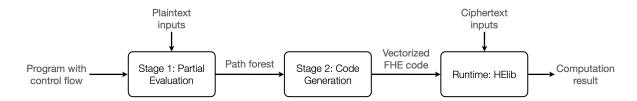

| 5.1  | COIL pipeline                                                                                                                                                                                                                                                                                                                                                                                                                                    | 94   |

| 5.2  | COIL snippet implementing associative array by using the index of a private key to look up a value                                                                                                                                                                                                                                                                                                                                               | 95   |

| 5.3  | Applying the path forest evaluation technique to Figure 5.2                                                                                                                                                                                                                                                                                                                                                                                      | 98   |

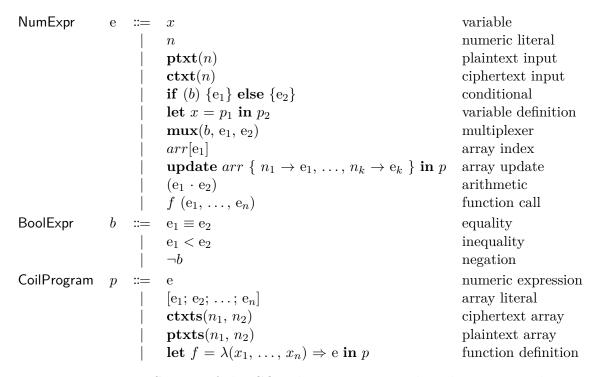

| 5.4  | Syntax of the COIL language. Note that the $\mathbf{mux}$ production is only added for use in Section 5.2.5, and is not directly used in any of our benchmarks                                                                                                                                                                                                                                                                                   | 100  |

| 5.5  | Syntax of the path forest IR. Note that Expr technically also includes the other syntactic forms from COIL programs, but the compilation process eventually rewrites all of these to one of the final forms listed in the grammar                                                                                                                                                                                                                | 101  |

| 5.6  | The transformations done by the COIL compiler are implemented in the $\llbracket \cdot \rrbracket_U^{\Gamma}$ operator, which successively rewrites terms in the path forest IR. $\Gamma$ is a context mapping variables to normal-form (let-free, if-free, and function-free) expressions. The rewrite rules for <b>update</b> and array indexing are similar to the rules for <b>let</b> -bindings and arithmetic, and are omitted for clarity | 101  |

| 5.7  | Snippet of a COIL program implementing a binary search over an array of encrypted data. While the language does not natively support division, the programmer can implement a midpoint function over plaintexts without incurring a run-time overhead                                                                                                                                                                                            | 103  |

| 5.8  | Grammar for decision forests                                                                                                                                                                                                                                                                                                                                                                                                                     | 109  |

| 5.9  | Decision tree computing a bounded GCD                                                                                                                                                                                                                                                                                                                                                                                                            | 112  |

| 5.10 | Running time of each benchmark. The reported COIL times include both the online and offline phase. Naïve merge times out after 30 minutes                                                                                                                                                                                                                                                                                                        | 115  |

| 5.11 | Example snippets merging two sorted arrays of ciphertexts in C++ and in the COIL surface language. Note that an actual implementation of merge would include bounds checks for the two indices i1 and i2; these checks have been omitted from the above code for the sake of clarity                                                                                                                                                             | 116  |

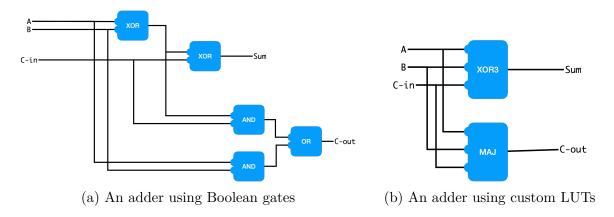

| 6.1  | Circuits can be made smaller by using custom LUTs instead of traditional Boolean gates                                                                                                                                                                                                                                                                                                                                                           | 123  |

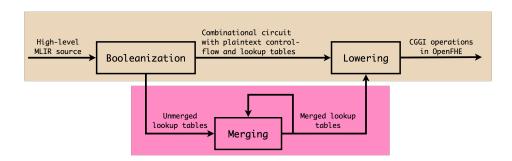

| 6.2  | Overview of Boolean FHE workflow. The red highlight denotes COATL's workflow                                                                                                                                                                                                                                                                                                                                                                     | 7125 |

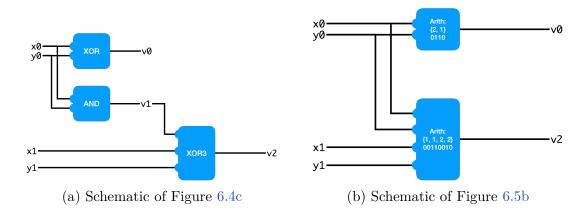

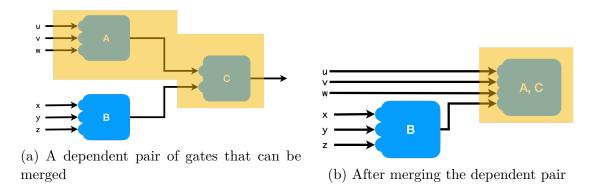

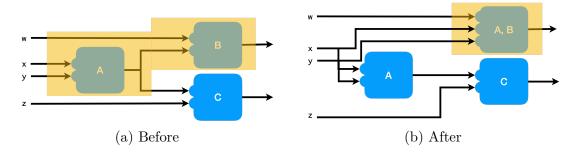

| 6.3  | COATL merges the AND with the XOR3 to produce a smaller circuit                                                                                                                                                                                                                                                                                                                                                                                  | 127  |

| 6.4  | Adding two encrypted 8-bit integers                                                                                                                                                                                                                                                                                                                                                                                                              | 129  |

| 6.5  | Applying COATL to the booleanized circuit in Figure 6.4b                                                                                                                                                                                                                                                                                                                                                                                         | 130  |

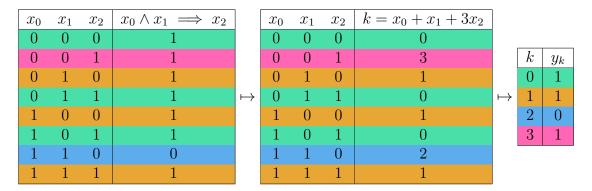

| 6.6  | Truth tables can be modeled using arithmetic LUTs                                                                                                           | 131 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.7  | A truth table can be mapped into a smaller arithmetic LUT by partitioning its rows, and then finding a linear combination that distinguishes the partitions | 133 |

| 6.8  | Merging can yield circuits with fewer gates                                                                                                                 | 134 |

| 6.9  | Merging a gate with multiple consumers only shrinks the circuit if all consumers are merged                                                                 | 136 |

| 6.10 | By changing the placement of the secret block, the programmer can control whether or not the loop gets unrolled                                             | 141 |

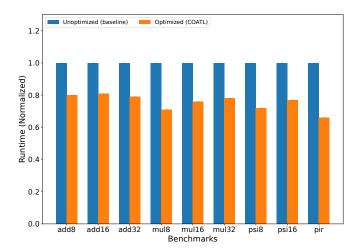

| 6.11 | Baseline vs COATL run times, normalized to baseline. 95% confidence intervals are plotted on the bar graph, but they are miniscule                          | 145 |

# **ABBREVIATIONS**

BFV Brakerski-Fan-Vercauteren

CGGI Chillotti-Gama-Georgieva-Izbachène

DSL Domain-Specific Language

FHE Fully Homomorphic Encryption

GDPR General Data Protection Regulation

HEIR Homomorphic Encryption Intermediate Representation

HIPAA Health Insurance Portablity and Accountability Act

IR Intermediate Representation

ISA Instruction Set Architecture

LUT Lookup Table

MLIR Multilevel Intermediate Representation

Mux Multiplexer

MPC Multiparty Computation

PBS Programmable Bootstrapping

RLWE Ring Learning With Errors

SIMD Single Instruction Multiple Data

SLP Superword-Level Parallelism

# **GLOSSARY**

Alignment The part of a vector schedule that describes which instruc-

tions (gates) are packed together

Arithmetic Circuit A circuit in which the wires hold integers and the gates

represent integer addition/multiplication

Arithmetic Lookup Table A multi-input lookup table in which the inputs are inter-

preted as an index into the table via a linear combination

Boolean Circuit A circuit in which the wires hold bits and the gates rep-

resent Boolean gates

Bootstrapping An operation in Fully Homomorphic Encryption schemes

that "refreshes" a ciphertext, allowing computation over

that ciphertext to continue

Control Flow The order in which program statements are executed

Ciphertext Describing an object that "contains" a (plaintext) value,

but is indistinguishable from a random value without the

secret key

Ciphertext Packing The ability of certain (RLWE-based) FHE schemes to pack

multiple plaintexts into a single ciphertext, and perform

computations element-wise

Circuit A directed acyclic graph in which vertices are *gates*, or sim-

ple functions being evaluated, and edges are wires dataflow

dependences between the gates.

Cryptosystem A set of algorithms for encrypting plaintexts and decrypt-

ing ciphertexts

Data Movement The instructions in a vector program that move data be-

tween lanes to align them for future vector operations

Decision Tree A program with branching control-flow, and a unique

control-flow path to each basic block

Fully Homomorphic Encryption Any cryptosystem that additionally provides the capabil-

ity to evaluate arbitrary finite circuits directly over cipher-

texts

Lane Placement The part of a vector schedule that describes the vector

lane on which each instruction (gate) produces its result

Lookup Table A unary function with domain a finite totally ordered set

such as  $\mathbb{Z}/p$  called the set of rows

Multiparty Computation Any cryptographic protocol that allows mutually distrust-

ful parties to collaboratively compute a known function

over their private inputs

Multiplexing A technique for linearizing branching control flow by eval-

uating both branches and then selecting a single result

Path Forest A data structure that annotates control flow paths

through a program with path-dependent information

Plaintext Describing a value that has yet to be encrypted, and does

not require a secret key to interpret

Programmable Bootstrapping The ability of CGGI to evaluate arbitrary (unary, nega-

cyclic) functions while bootstrapping

Protoschedule A vector schedule for a quotient of a circuit

Quotient (of a graph) A graph related to the original by contracting

the edges of a connected subgraph

Vector Lane A slot in a vector that can hold a single unit of data

Vector Schedule For a circuit, a choice of which gates get executed simulta-

neously, and an assignment of a vector lane on which the

output of each gate is produced

Vectorization A compiler pass that transforms a program expressed over

individual data elements into one expressed over packed

vectors of data

# ABSTRACT

In a world increasingly concerned with data privacy, the availability of privacy-preserving computation is more important than ever. Unfortunately, the widespread adoption of powerful cryptographic techniques such as Multiparty Computation (MPC) and Fully Homomorphic Encryption (FHE) is limited by the great deal of expertise they require, and their lack of easy programmability. Alleviating this burden of expertise is the subject of much research from both the programming languages and cryptography communities, and is the goal of this dissertation. To this end, we introduce the philosophy of Compiler Cryptosystem Co-Design, which posits that in order to achieve this goal, we need to build compilers that understand the target cryptosystem, and simultaneously develop cryptosystem abstractions tailored to the compiler rather than the programmer.

We justify the above claim by presenting four increasingly ambitious examples of applying Compiler Cryptosystem Co-Design to problems in the domain of Fully Homomorphic Encryption computations: Coyote, COPSE, COIL, and COATL. In Coyote, we build a compiler with enough context to understand the subtleties of FHE vectorization, and demonstrate how this allows it to outperform traditional vectorization techniques. With COPSE we explore the other side of this philosophy via a highly vectorizable cryptographic abstraction that encodes the branching structure of (encrypted) decision trees; We show how to use this abstraction to accelerate an otherwise difficult-to-parallelize problem like secure decision forest inference. In COIL we push the idea of "co-design" to its natural conclusion by combining the insights from the previous two examples in a language for expressing secure computations that contain nontrivial control flow. Finally, with COATL we go a step further, changing the underlying programming model of the cryptosystem while developing compilation techniques to perform optimizations that were previously inexpressible.

We conclude by observing that although this dissertation represents an important step towards making privacy preserving computation universally accessible, the ideas contained therein barely scratch the surface of what is possible with compiler cryptosystem co-design; we present two interesting future directions to explore.

### 1. INTRODUCTION

Whether it is to protect intellectual property, as in the case of secure machine learning, or to comply with governmental data privacy regulations like HIPAA or GDPR, or simply to defend against unwanted data breaches, we often need to write *privacy-preserving applications* that can perform computations without learning anything about their inputs.

A popular approach to writing privacy-preserving software is Multiparty Computation (MPC), a class of cryptographic protocols that allow mutually distrusting parties to jointly compute functions over private inputs without sharing those inputs with each other. While MPC protocols are, in theory, powerful enough to evaluate any (bounded, terminating) function, actually writing practical programs that use MPC has a few drawbacks:

- The high cryptographic overhead of MPC sometimes makes nontrivial programs prohibitively expensive to evaluate

- The MPC programming model can be highly counterintuitive, making it very difficult for non-experts to write efficient MPC programs

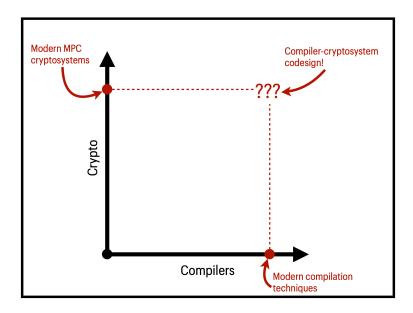

**Figure 1.1.** Compiler Cryptosystem Co-Design can bridge the gap between sophisticated but crypto-agnostic compiler analyses, and modern cryptosystems with rich capabilities.

### **MPC-Aware Compilers**

Compilers naturally suggest themselves as a solution to both these problems: By treating the low-level MPC primitives as a fixed instruction set to target, we can allow programmers to express their computations in a high level language, and automatically lower them down to our "MPC instruction set". Of course, this is by no means a novel insight; the literature is littered with examples of MPC languages and compilers that mechanically translate insecure operations into their secure MPC equivalents, but do very little optimization on top of this [1–10]. This is essentially how traditional compilers worked in the 1980s—translating high-level languages into assembly one line at a time—but compilation techniques have come a long way since then, and optimizations like smart instruction selection and vectorization are practically standard in any modern production-quality compiler (as illustrated on the horizontal axis of Figure 1.1).

Unfortunately, applying techniques like these to the MPC space can be highly nontrivial. Consider, for example, Superword-Level Parallelism (SLP), a technique for automatically vectorizing programs even in the absence of structures like for-loops [11–13]. Vectorizing compilers that use SLP typically target vector instruction sets in CPUs, and SLP therefore bakes in certain assumptions about the cost model of these instructions. A naive attempt at applying SLP-style vectorization to MPC programs fails for essentially this reason: While some MPC schemes do support a limited form of vectorization called *ciphertext packing*, their programming model is vastly different from that of CPU vector architectures. In particular, the lack of easy vector shuffle/select instructions means that SLP-vectorized code can easily perform *worse* than its scalar counterpart—a phenomenon discussed in more detail in Chapter 3, in which we develop techniques to adapt SLP-style vectorization to the MPC domain. The takeaway is that just as a good compiler engineer needs to have a deep understanding of the target architecture, *writing a good MPC compiler requires a deep understanding of the semantics and cost model of the target MPC scheme!*

### Compiler-Aware MPC

The story so far is reasonably satisfying: We can build compilers with a "baked in" understanding of MPC-specific optimizations, turn these loose on our privacy-preserving programs, and go home with the satisfaction of having tried our best. But just as compilation techniques have gotten more sophisticated in the past decades, cryptographers have simultaneously built multiparty cryptosystems with increasingly complex capabilities—capabilities that are incredibly difficult to directly reason about and take advantage of, as depicted along the vertical axis of Figure 1.1. To get around this, modern cryptosystems often provide simpler abstractions for programmers to use instead of directly interacting with the underlying protocols. A classic example is programmable bootstrapping (PBS): an operation that some MPC schemes support that allows directly evaluating a certain class of functions on encrypted values. Manually mapping computations down to these functions turns out to be quite challenging, so most implementations of PBS cryptosystems also provide a pre-built library of operations (usually a handful of Boolean gates) for programmers to use, thus trading off flexibility for programmability. However, as we discuss in more detail in Chapter 6, this greatly undersells the cryptosystem's capabilities. Indeed, by designing abstractions for the *compiler* instead of the *programmer*, we can avoid giving up this flexibility and still generate better code.

#### Compiler Cryptosystem Co-Design

Generalizing the insight from above, we arrive at the central premise of this dissertation: It is not enough to simply think of the cryptosystem as a fixed instruction set to target, nor is it enough to treat the compiler as a naïve translator from high-level programs to MPC operations. Instead, we need to build MPC-aware optimizing compilers while simultaneously tweaking the protocol to provide better abstractions for our MPC compilers, a philosophy we refer to as compiler cryptosystem co-design, and which fills in the upper-right corner of Figure 1.1. In this dissertation we explore what compiler cryptosystem co-design looks like for a particular class of MPC protocols known as Fully Homomorphic Encryption, or FHE.

We start by describing existing languages and compilers for MPC, and then present a number of novel works that use the philosophy of compiler cryptosystem co-design to improve on the current state-of-the-art.

#### 1.1 Languages & Compilers for MPC

To understand and appreciate the novelty of our contributions in compiler cryptosystem co-design, it is essential to first survey the broader landscape of languages and compilers for MPC. Much of the early work in this space (e.g. Wysteria/Wys\* [2, 3], HACCLE [14], Viaduct [15]) focuses not on performance, but on how to express programs in MPC in the first place. These works develop techniques to "extract" secure subcomputations based on information flow requirements, reason about complicated protocol-specific capabilities to select the correct MPC backend for each subcomputation, and verify both the correctness and security of the final generated code (e.g. by reasoning about the composability of the different protocols used). Such techniques serve to alleviate much of the burden of true "multiparty" programming, in which "mixed-mode computations" (ones that switched between secure and insecure phases, and between different MPC protocols) are not only possible, but unavoidable.

The early FHE space looks vastly different. Practically all FHE schemes consist of only two parties: A "client" encrypts their data with a private key and sends the ciphertexts to an "evaluator," who uses a public "evaluation" key to perfom homomorphic computations. Multiparty schemes do exist, but largely work via a "key exchange" protocol in which multiple clients collaborate to agree on a single evaluation key, before sending it to the evaluator along with their ciphertexts and proceeding as normal. Thus, reasoning about complicated information flow requirements is largely not required. Together with the fact that "scheme-switching" in the style of CHIMERA [16] and PEGASUS [17] was still several years away at this point, this means that the early developments in MPC languages didn't necessarily translate into better languages for FHE.

Instead, FHE compiler developers begin to focus on an orthogonal set of problems; ones that affect not correctness, but performance. A major challenge with optimizing FHE programs is how opaque the cost models are: Forgetting to relinearize a ciphertext may not affect the result of a computation, but it can cause the program to slow to even more of a crawl than before. As a result, we begin to see compilers that focus on good automatic translation, allowing programmers to write the logic of their application without worrying about such low-level details. Seminal works in this space include CHET [18], which automatically selects appropriate ciphertext layouts for tensor programs; EVA [10], which reasons about complicated cost models to insert important ciphertext maintenance operations like bootstrapping, rescaling, and relinearization; and Ramparts [1] and ALCHEMY [9], which supply programmers with efficient implementations of higher-level homomorphic kernels, and handle tedious tasks such as parameter selection. Crucially, although these techniques do significantly improve performance, they perform very few other optimizations, and essentially preserve the original structure of the program.

Recent years mark the emergence of compilers that finally cross this barrier to perform nontrivial optimizations on their source programs. These compilers can be classified into two camps: those that perform optimizations automatically, and those that require some programmer effort. In the first camp are works like the TFHE Transpiler [19] and its successor, the HEIR framework [20], which use hardware synthesis tools like XLS [21] and Yosys [22] to generate efficient FHE circuits and leverage the power of MLIR [23] to perform a number of standard optimizations; Fhelipe [24], which determines good data layouts for a program written in a Numpy-style DSL; and Concrete [25], which performs a number of rewrites on the computation graph extracted from a python program before generating code. In the other camp are works like Porcupine [26], which vectorizes FHE computations but requires the programmer to provide a sketch to constrain rotation patterns; and a number of DSLs like HECO [20] and Airduct [27] that require the programmer to express their computations in a restrictive array language to assist in vectorization.

#### 1.2 Contributions

The ideas in this dissertation are organized into four chapters, each of which uses compiler cryptosystem co-design to tackle a different problem in the world of secure computation:

- We start by addressing the problem of FHE-aware vectorization in Chapter 3. Certain FHE schemes support a technique allows computations to be expressed over packed ciphertext vectors (Section 2.3.1) rather than individual ciphertexts. However, the unique semantics and cost models of these schemes mean can render traditional (SLP-based) approaches to vectorizing ineffective, often causing them to degrade performance rather than improving it. We present Coyote, the first compiler that FHE-specific cost models and heuristics to vectorize FHE programs. We show that Coyote consistently outperforms traditional SLP-style techniques, and even often discovers schedules that match the best expert-written implementations for some kernels.

- While Coyote considers arbitrary straight-line programs, in Chapter 4 we shift our attention to the special case of vectorizing secure control flow in the form of decision forests (Section 2.2). We present COPSE, an abstraction that sits on top of existing FHE cryptosystems and encodes the control flow of a decision forest as a series of highly vectorizable matrix operations. We demonstrate that using the COPSE abstraction to vectorize decision forests can accelerate inference by up to an order of magnitude.

- Chapters 3 and 4 consider vectorizing straight-line code and control flow separately, but real programs often contain both. In Chapter 5 we investigate how to combine these ideas in COIL, a language for expressing secure computations that contain both straight-line code and ciphertext-dependent branches. Along the way, we develop the idea of path forests, a novel intermediate representation for secure branching, and show how path forests unlock a number of optimizations that would not otherwise be possible with the usual multiplexing strategy.

- In Chapter 6 we finally depart from talking about vectorization and control flow to explore the depths of compiler cryptosystem co-design with COATL. Where COPSE built abstractions on top of existing cryptosystems, COATL changes the programming abstraction the cryptosystems provide and then develops novel compilation techniques to target the new abstraction. The particular cryptosystems we consider in this chapter are Boolean FHE schemes, in which ciphertexts are encryptions of bits, and computations

correspond to homomorphically evaluating Boolean gates. We present the arithmetic lookup table—a cryptographic abstraction that replaces Boolean gates—and develop compilation techniques to generate circuits built from these tables. We demonstrate that our techniques can take full advantage of existing machinery to synthesize and optimize Boolean circuits, but still generate circuits up to  $1.5\times$  smaller than their already-optimized Boolean counterparts.

The remainder of this dissertation is organized as follows: Chapter 2 develops necessary background and formalisms, Chapters 3-6 present our main contributions as described above, and Chapter 7 concludes by discussing some possible future directions to explore.

# 2. BACKGROUND

We provide here most of the background necessary to understand the chapters that follow, rather than dispersing it throughout.

#### 2.1 Vectorization

Single instruction, multiple data, or SIMD, is a way of amortizing the run-time complexity of a program by vectorizing it, or lifting its scalar computation to one that operates over packed vectors. To vectorize, we need to first find sets of isomorphic scalar instructions and then decide how to pack the scalar operands of those instructions into vectors before replacing all of them with a single vector instruction. In traditional SIMD, this process relies heavily on the presence of data-parallel loops in the original program. Unrolling the loop by a few iterations (usually four or eight) produces a set of isomorphic instructions, one for each unrolled iteration. These are then packed into vectors, with one iteration per vector slot, and lifted into vector instructions. Thus, a loop that performs a scalar computation N times can be lifted into one that performs a semantically equivalent vector computation N/4 times.

Superword-Level Parallelism (SLP) is a more general technique that does not rely on the presence of loop-based control structures in the program to find vectorizable instructions. SLP analyzes a whole sequence of scalar instructions at once, looking for sets of available instructions (instructions whose operands have already been scheduled) that are all isomorphic to each other. At each step, it picks such a set and packs its instructions together into a vector, scheduling them together.

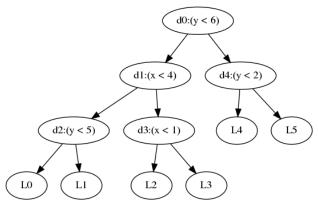

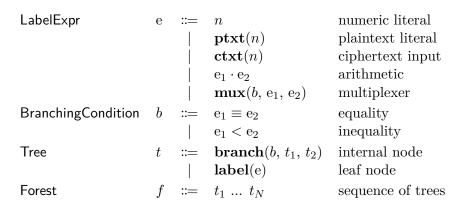

Figure 2.1. Example decision tree

#### 2.2 Decision Forests

A decision tree is a classification model that assigns a class label to a vector of features by sequentially comparing the features against various thresholds. Figure 2.1 shows an example of a single decision tree. Inference over a decision tree is recursive. Leaf nodes of the tree correspond to class labels, whereas each interior "branch" node specifies a feature and a threshold. That feature from the vector is compared against the threshold, and depending on the result of the comparison either the left or right child of the tree is evaluated. For instance, the tree in Figure 2.1 uses x and y as its features and assigns class labels  $L_0 - L_5$ . Assuming the left branch is taken when the decision is false and the right branch is taken when true, the tree assigns the input feature (x,y) = (0,5) to the class label  $L_4$ . A decision forest model consists of several decision trees over the same feature set in parallel. Inference over a decision forest usually consists of obtaining a class label from each individual tree, and then combining the labels in some way (either by averaging or choosing the label selected by the plurality of trees, or some other domain-specific combining function).

#### 2.3 Fully Homomorphic Encryption

Fully Homomorphic Encryption refers to a class of encryption schemes that allow for homomorphic computation over ciphertexts; e.g., the sum or product of the encryptions of two integers is the encryption of their sum or product. FHE is a useful cryptographic tool

for carrying out *privacy-preserving* or *oblivious computation* (evaluating programs where the inputs are unknown to the evaluator).

A common use-case for FHE is *computation offloading*, which uses a single public/private keypair and only involves two parties<sup>1</sup>. The client encrypts their inputs to a program with their private key and sends the ciphertexts to the evaluator. The evaluator uses the public key to evaluate the program via a sequence of homomorphic operations before sending the result ciphertext back to the client, who finally decrypts it and learns the output of the program.

FHE schemes are often classified by how they model ciphertexts. In *arithmetic* schemes, ciphertexts represent encryptions of integers modulo some fixed large prime p. In *Boolean* schemes, ciphertexts are usually thought of as encryptions of bits.

#### Limitations

While FHE is a powerful technology that enables privacy-preserving computation, its lack of easy programmability prevents it from seeing widespread use. Because of the nature of secure computation, FHE does not support branching over ciphertexts—conditionals cannot depend on the values of encrypted data, otherwise the path taken through the computation leaks information about the data. In particular, this precludes FHE computations from having any kind of control flow structures, including conditionals and loops, that are control-dependent on ciphertexts. Applications must be expressed directly as *circuits* that transform ciphertexts using the homomorphic operations provided by the underlying FHE scheme: usually integer addition and multiplication for arithmetic schemes, or a fixed set of Boolean gates for Boolean schemes.

Furthermore, FHE is *slow*. Even in state-of-the-art FHE implementations, the cryptographic overhead of a single homomorphic operation can be multiple orders of magnitude greater than that of performing the same operation over unencrypted values. Naïvely translating a plaintext function into its ciphertext equivalent can produce circuits that are too

$<sup>^{1}</sup>$ ↑Some authors have proposed multiparty multi-key extensions to FHE [28–30]. While we do not directly make use of these, the ideas in this dissertation are relatively straightforward to extend to a multikey setting.

expensive to evaluate on any nontrivial inputs; Writing efficient FHE programs requires a great deal of cryptographic expertise.

#### 2.3.1 Ciphertext Batching

One way to mitigate the overhead of encrypted computation is via *ciphertext batching*, an optimization that certain (RLWE-based<sup>2</sup>) FHE schemes provide [31, 32]. Ciphertext batching allows encrypting a vector of integers into a *single* ciphertext in such a way that homomorphic operations occur element-wise on the underlying vector (i.e. SIMD-style).

This style of vectorization has a few peculiarities that distinguish it from normal vectorization:

- 1. The vectors are much larger than traditional hardware vector registers (e.g. several thousand slots wide, compared to the usual 4 or 8 slots). Utilizing this much space poses unique challenges.

- 2. Unlike with physical vector registers, there is no *indexing* primitive that can directly access a value in a particular slot of a ciphertext vector.

- 3. In general, the only way to move data between vector slots is by cyclically permuting its contents. This makes it much more important to assign vector lanes to packed instructions optimally, since realizing arbitrary permutations by composing several rotations quickly gets computationally expensive.

The challenges posed by points (2) and (3) in particular preclude directly using SLP-style vectorization, since its local reasoning means it does not sufficiently consider the high cost of data movement between lanes when deciding what instructions to pack together. Chapter 3 discusses this in more detail.

$<sup>^2\</sup>uparrow$ RLWE stands for Ring Learning with Errors, a number-theoretic problem that involves distinguishing two distributions of polynomials. The security of FHE schemes such as BFV and BGV (the one used in this chapter) is based on the hardness of RLWE.

#### 2.3.2 Bootstrapping

Much of the security of FHE schemes comes from a small amount of noise added to each ciphertext upon encryption. A freshly encrypted ciphertext starts with a certain *noise budget*. When the noise level exceeds this budget, it interferes with the encrypted value, causing decryption to fail. Homomorphic operations—in particular, multiplication—accumulate noise; hence, the noise budget roughly corresponds to the *maximum depth* of circuit that can be evaluated. The noise budget can be increased by encrypting into larger ciphertexts, which are in turn much slower to compute over.

Alternatively, some schemes support a technique called *bootstrapping* [33, 34] which "refreshes" the noise budget by homomorphically evaluating the decryption function. Unfortunately, bootstrapping is incredibly slow, and also carries some limitations governing when it can be used. Managing the total depth is, therefore, crucial to designing efficient FHE applications.

#### 2.3.3 CGGI

The CGGI scheme [35] supports encrypting n-bit integers for some small n (usually 2 or 3). CGGI natively supports ciphertext addition and scaling ciphertexts by a known plaintext constant. Unlike many of its FHE counterparts, however, it also supports a technique called programmable bootstrapping. Unlike a traditional bootstrap, which resets the noise values in a batch of ciphertexts without changing the underlying encrypted values, a programmable bootstrap can only operate on one ciphertext at a time, but additionally evaluates an arbitrary unary function (usually represented as a  $2^n$ -row lookup table) on the encrypted value.

In most implementations of CGGI, these lookup tables are used to capture classic Boolean truth tables: a  $2^n$ -row lookup table can represent a truth table with n inputs. In other words, these lookup tables are abstracted as n-input Boolean gates, with ciphertext inputs treated as bits.

A key observation we make in Chapter 6 is that while this abstraction facilitates easy circuit construction (as various Boolean circuit optimization techniques can be applied), it undersells the flexibility of CGGI's lookup tables. In actuality, ciphertexts in CGGI are

encryptions of integers mod p, where p is the size of the lookup table, and the lookup tables index the result of linear combinations of the ciphertext inputs. (Section 6.2.1 provides a more formal treatment of this fact.) It is precisely this additional flexibility that we exploit in Chapter 6 to build more complex lookup tables and hence create circuits with fewer gates. Note that the number of gates in the circuit is the main metric that matters for performance: while programmable bootstrapping is a more lightweight technique than traditional (batched) bootstrapping, it is still far more expensive than any other CGGI operation. Thus, the latency of a CGGI circuit is almost entirely determined by the number of bootstraps—and hence, the number of gates—it contains.

### 2.4 MLIR/HEIR

MLIR[23] is a compiler infrastructure that aims to simplify the process of writing domainspecific compilers. It allows compiler authors to define "dialects" of custom IR operations,

and easily implement "passes" that transform code between these dialects. HEIR[36] is a

fork of MLIR that adds a number of FHE-specific dialects and passes, such as a generic

secret dialect for representing arbitrary homomorphic computation, and several schemespecific dialects including one for CGGI. HEIR also implements several passes for lowering

programs written using the secret dialect into scheme-specific operations and generating

code for a target FHE implementation. We implement the ideas in Chapter 6 on top of

the HEIR infrastructure, and in particular, on top of an existing pipeline of passes that

transform secret code into circuits built out of 2- to 3-input Boolean gates, lower these

gates into CGGI operations, and then generate code for the OpenFHE library [37]. This

pipeline performs some optimizations on the Boolean circuit before lowering to CGGI, but

these optimizations stay in the realm of Boolean gates, and do not take advantage of any of

the CGGI-specific techniques we discuss in Chapter 6.

#### 2.5 Circuits & Multiplexers

The standard security guarantee for oblivious computation is *noninterference*: an evaluator without the private key cannot distinguish two traces of a program that differ only in

encrypted variables. This poses a problem for programs with branching: in knowing which branch to take, the evaluator must learn something about any ciphertext that influences that branch, breaking noninterference. To preserve noninterference we want programs to exhibit oblivious control-flow semantics, in which the evaluator can correctly execute a branching program without knowing anything about which branches were taken.

A common way to provide such semantics is via secure multiplexers ("muxes"), cryptographic operations that use a ciphertext selector to obliviously choose between multiple inputs, returning the input corresponding to the value of the selector<sup>3</sup>. When the evaluator encounters a branch, it executes both paths, and then uses the branching condition and a mux to select the correct value when control flow converges. This obviates the need to reveal anything about the branching condition to the evaluator, and still ensures that the correct return value is produced. Note that this technique can in the worst case have an exponential effect on the total computation time: every path through the program has to be evaluated, even if the result of only one is used.

The use of muxes can be extended to other kinds of secure control flow such as loops: given a plaintext upper bound on the number of iterations, a loop can be fully unrolled into a series of branches that check the exit condition for each iteration, which can be obliviously evaluated as above.

$<sup>3\</sup>uparrow$ An example of a mux in an FHE scheme that provides homomorphic addition and multiplication is  $\underline{b}X + (1 - \underline{b})Y$ , where  $\underline{b}$  is the (ciphertext) selector bit, and X and Y are the two inputs being selected between.

# 3. COYOTE

The Coyote is limited, as Bugs is limited, by his anatomy.

Chuck Jones

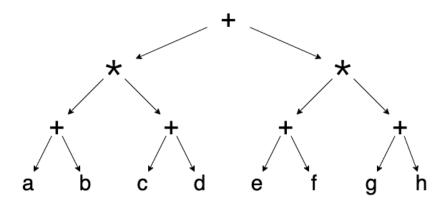

Figure 3.1. An example of an arithmetic circuit

In this chapter we develop a vectorization technique that is "FHE-aware"; That is, it understands the unique cost models and semantics of ciphertext packing. A natural first question to arise is: Why do we need an FHE-aware technique at all? Techniques like Superword-Level Parallelism (SLP) have existed for decades [13] and perform remarkably well in the classical vectorization space. Unfortunately, a naïve application of these techniques to FHE circuits fails. SLP aggressively packs isomorphic instructions into vectors, assuming that shuffling vector lanes around or indexing into a vector is relatively cheap. While this is a reasonable heuristic when targeting a physical vector architecture, FHE vectors are not hardware registers with slots for data; instead, the only way to move data between "vector lanes" is by performing a cyclic rotation of the entire vector. Realizing the shuffles incurred by SLP with a series of masks and rotations is expensive, and can quickly outweigh any benefits from vectorizing, as demonstrated below.

```

%0 = a + b

%1 = c + d

[\$0, \$1, \$3, \$4] = [a, c, e, q] +

%2 = %0 * %1

[b, d, f, h]

[%2, _, %5, _] = [%0, _, %3, _] *

%3 = e + f

[%1, _, %4, _]

%4 = q + h

[%6, _, _, _] = [%2, _, _, _] +

%5 = %3 * %4

%6 = %2 + %5

(a) No vectorization

(b) Aggressive vectorization, incurs two rotates

[%1, %3] = [c, e] + [d, f]

[\$0, \$4] = [a, g] + [b, h]

[\$2, \$5] = [\$0, \$3] * [\$1, \$4]

[%6, _] = [%2, _] + [%5, _]

(c) Optimal schedule, incurs one rotate

```

Figure 3.2. Possible schedules for Figure 3.1

# The Vectorization/Rotation Tradeoff

Consider the arithmetic circuit<sup>1</sup> in Figure 3.1 implementing ((a + b) \* (c + d)) + ((e + f) \* (g + h)). Applying SLP yields the schedule in Figure 3.2b, which packs together the four additions at the first level, and the two multiplies at the second level. The resulting schedule has a vector add, followed by a vector multiply, followed by an add. Rotations are needed between each operation to align the outputs of each operation with the next. Using an approximate model<sup>2</sup> of the relative latencies of each instruction in which multiplies and rotates have a latency of 1 and addition has a latency of 0.1, the total cost of this schedule is 3.2. However, by doing no vectorization and executing the circuit entirely with scalar operations (Figure 3.2a), we have five adds and two multiplies, with an overall cost of 2.5. In this case, vectorization actually makes the performance worse! The schedule in Figure 3.2c shows how we can do better: We pack the a+b and the e+f adds separately from the c+d

¹↑We adopt the FHE-standard representation of arithmetic circuits as the intermediate representation for our programs [1, 26, 33, 38].

<sup>&</sup>lt;sup>2</sup>↑Algorithms in HElib [39] assigns a "high latency" to both multiplies and rotates and a "low latency" to adds. For both simplicity and concreteness, we assume a 10:1 ratio between "high latency" and "low latency."

and g + h adds, so that neither of them require a rotation to align with the multiply above them. By saving one rotation at the cost of an extra vector addition, we get a schedule with an overall cost of only 2.3. Clearly, we need a new vectorization strategy, and in particular, one that can properly account for the high cost of data movement throughout the program.

#### Co-optimization of Vector Packing and Data Layout

The main obstacle to optimality when using the classical SLP approach comes from the high cost of permuting vector elements: Aggressively packing instructions into vectors can require substantial and complex data movement to align operands for downstream vector instructions (e.g., SwizzleInventor [40] resorts to sketch-based synthesis to generate the appropriate permutations); Thus, such a schedule can incur so much overhead that no amount of vectorization makes it worth it.

More recent takes on SLP, such as VeGen [12] and goSLP [11], recognize the need to take the cost of data movement into account. VeGen, for instance, can decide to not pack certain instructions together because the data movement cost incurred is not worth it. However, VeGen does its reasoning *locally*; that is, it cannot reason about the effect packing instructions together may have on shuffling costs much later in the program. This tradeoff, fine in circumstances when shuffling is relatively cheap, is inappropriate for FHE, where shuffling is very expensive. While goSLP does reason globally, the cost model it uses to avoid overpacking is incompatible with the semantics of FHE vectorization. We discuss both of these techniques further in Section 3.5.

Our key insight is that because rotations are so expensive, data layout and vector packing are fundamentally intertwined; rather than treat these as separate problems, we must optimize them together when finding a schedule. In this chapter, we develop an approach that works at the level of subcircuits, splitting the program up into smaller pieces within which all the computations are locked into a single lane to avoid doing any rotations at all. While vectorizing across subcircuits gives up some packing potential (because operations within a subcircuit cannot be vectorized together), the savings on rotation costs can make up the difference: the subcircuits prevent over-vectorization that incurs too many rotations.

The optimal schedule of Figure 3.2c can be viewed as grouping (a + b) with its downstream multiply in one subciruit, and (g + h) with its downstream multiply in another subcircuit, and then vectorizing those two subcircuits together.

This approach yields a natural question: how do we decide which computations to merge into a subcircuit? This seems circular: subcircuit merging is intended to yield fewer rotations, which are determined by data layout, and data layout is driven by which operations are vectorized together, which in turn is constrained by subcircuit identification.

#### Contributions

We present Coyote, the first FHE-aware compiler that automatically vectorizes arbitrary arithmetic circuits. Coyote breaks the circular dependence between vector packing and data layout by using an iterative process that alternates between making packing decisions and determining data layout. Coyote uses simulated annealing to find optimal data layouts, and uses these to guide a best-first search towards optimal vector packs. Crucially, Coyote uses layouts from previous iterations of scheduling to identify subcircuits that would be profitable to merge, and then re-schedules based on the new subcircuits.

The specific contributions we make in this chapter are are:

- 1. An algorithm for simultaneously searching the space of data layouts and the space of vector packings to find an efficient combination.

- 2. A lightweight Python embedded DSL called Coyote, with a compiler that uses this algorithm to generate efficient FHE code for arbitrary programs

We test Coyote by using it to compile six computational kernels (matrix multiply, point cloud distances, 1D convolution, dot product, sorting a list, and finding the maximum element of a list), and compare the performance of the vectorized code to to the original unvectorized code. We also randomly generate several irregular polynomial-evaluation programs to measure the effect of things like operation density on Coyote's ability to vectorize. We find that Coyote yields efficient vector schedules with optimized rotations, and often recovers known-optimal expert implementations for certain kernels.

# 3.1 Coyote Overview

Figure 3.3. High-level compilation steps

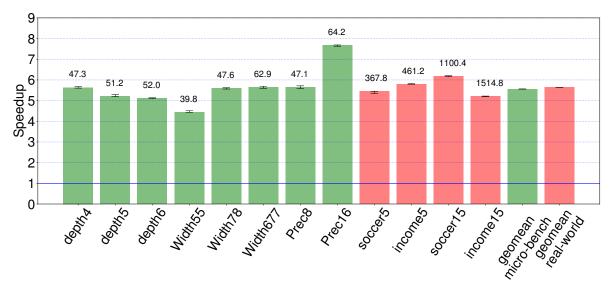

Figure 3.4. A running example of how Coyote vectorizes arbitrary arithmetic circuits

Coyote provides an embedded DSL (eDSL) that allows programmers to use a high level language to express computations in FHE. This computation is translated into an arithmetic circuit representing the computation, which is then compiled into vectorized FHE code. The process of compiling a circuit into vectorized code is shown in Figure 3.3, and described in more detail below, using the circuit in Figure 3.1 as a running example.

# 3.1.1 Compilation

- 1. Coyote quotients an input circuit (collapses subcircuits into single vertices) and assigns lanes to resulting vertices to produce a protoschedule that can be realized into a more efficient vector program. The result is a graph whose vertices correspond to connected subgraphs of the original circuit, such that no two vertices at the same height have the same lane (and hence are eligible to be vectorized together). Coyote collapses a subcircuit when it determines that the overhead of internally vectorizing it is not worth the gain from vectorization, so this step essentially forces certain operations to happen in scalar on a single lane. Section 3.2.2 describes how Coyote makes this decision.

- In the example in Figure 3.4a, the circled pairs of vertices are collapsed, yielding the quotient circuit in Figure 3.4b. The lane assignment for this protoschedule puts each un-quotiented addition on the same lane as its quotiented parent, and chooses one of these lanes on which to place the root of the tree.

- 2. The (collapsed) vertices at each height are aligned to pack together isomorphic nodes, producing a vector schedule from the protoschedule. In the example, the two adds at height 1 get trivially aligned, and the two "supernodes" at height 2 get aligned by packing together the two adds and the two multiplies. No alignment is needed for the single vertex at height 3. The details of the alignment procedure are given in Section 3.2.4. Figure 3.4c shows the result of this alignment.

- 3. Coyote compiles the schedule into a vector IR. The crux of this compilation step is figuring out when to blend and rotate. When a vector operand requires values from several different instructions, Coyote emits code to "blend" the results together into a single vector. When the lane an operand is used in is different from the lane it was produced in, Coyote emits a rotation instruction to move the operand into the correct lane. Notice that each arc in the protoschedule connecting vertices of different lanes corresponds to a rotation in the generated vector IR. Figure 3.4d shows the vector code Coyote generates for our running example. Notice that the generated code contains

two blends and one rotate. The blends are necessary<sup>3</sup> because on line 3 of the schedule, %0 and %3 are used in the same vector despite being produced in two separate vectors. Since none of the operands need to shift lanes, the vector instruction t0 = blend(v0@10, v1@01) takes [%0, %4] and [%1, %3] and blends them together to produce [%0, %3], which is exactly the operand used on line 3. Coyote emits a rotation because %5 gets used on a different lane than it is produced. The vector instruction  $s0 = v2 \gg 1$  takes [%2, %5] in v2 and produces [%5, %2] in s0. Section 3.3.1 describes the specifics of code generation.

```

def dot(v1, v2):

return sum([a * b for a, b in zip(v1, v2)])

@coyote.define_circuit(A=matrix(3, 3), b=vector(3))

def matvec_multiply(A, b):

result = []

for i in range(len(A)):

result.append(dot(A[i], b))

return result

```

Figure 3.5. Coyote program for multiplying a vector by a matrix

### 3.1.2 DSL

A programmer can use Coyote's DSL (shown in Figure 3.5) to specify a computation and generate an arithmetic circuit. The DSL exposes a number of ways to annotate inputs to the computation: replication, packing, and fixing a layout. Annotating an input with "replicate" indicates that a copy of the input should be passed to the circuit for each place it is used (ensuring that each copy gets used exactly once). By default, inputs are unreplicated, meaning that an input that gets used in multiple places will have a fan-out corresponding to its usage frequency.

Specifying a "packing" constraint for a set of inputs requires that they be packed into a single input vector in the final circuit (note that inputs in the same vector are necessarily in

$<sup>^3</sup>$ \tau We could, of course, simply exchange the positions of %3 and %4 and elide the blends. While Coyote does automatically perform this rewrite, we leave the blends in here for the sake of example.